### LM98714

# Three Channel, 16-Bit, 45 MSPS Digital Copier Analog Front End with Integrated CCD/CIS Sensor Timing Generator and LVDS Output

# **General Description**

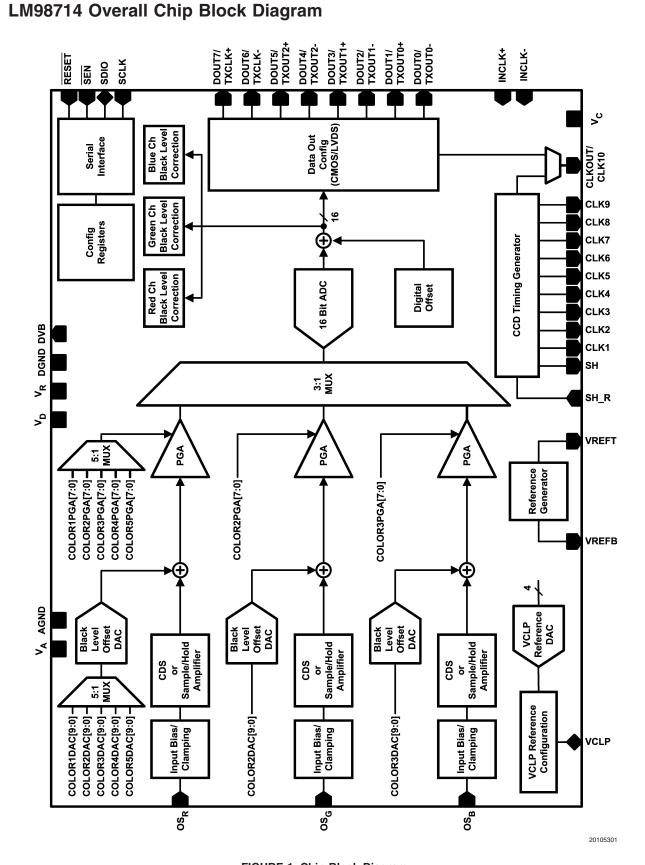

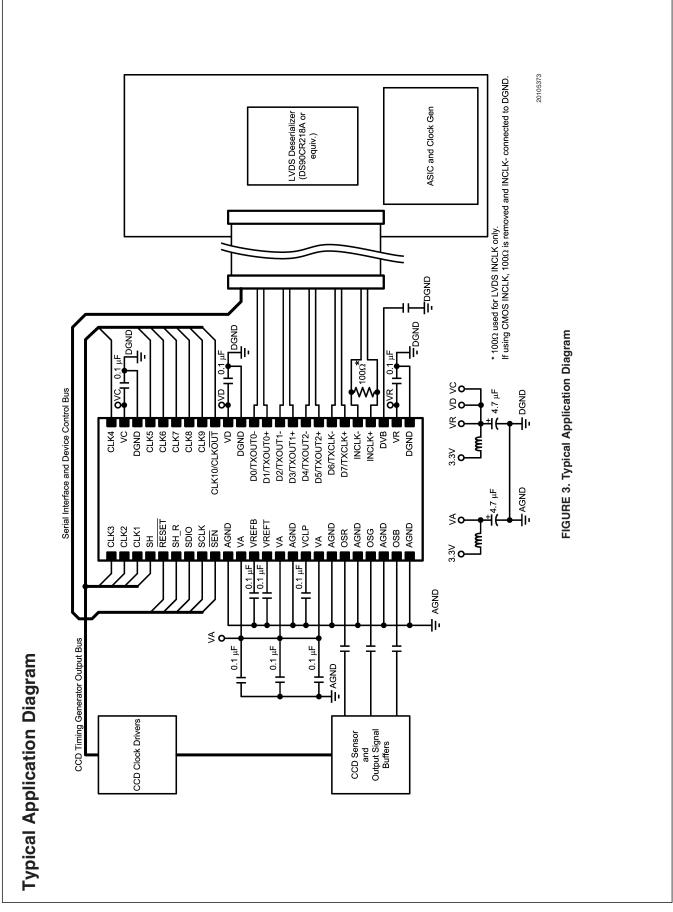

The LM98714 is a fully integrated, high performance 16-Bit, 45 MSPS signal processing solution for digital color copiers, scanners, and other image processing applications. Highspeed signal throughput is achieved with an innovative architecture utilizing Correlated Double Sampling (CDS), typically employed with CCD arrays, or Sample and Hold (S/H) inputs (for Contact Image Sensors and CMOS image sensors). The signal paths utilize 8 bit Programmable Gain Amplifiers (PGA), a +/-9-Bit offset correction DAC and independently controlled Digital Black Level correction loops for each input. The PGA and offset DAC are programmed independently allowing unique values of gain and offset for each of the three inputs. The signals are then routed to a 45MHz high performance analog-to-digital converter (ADC). The fully differential processing channel shows exceptional noise immunity, having a very low noise floor of -74dB. The 16-bit ADC has excellent dynamic performance making the LM98714 transparent in the image reproduction chain.

# **Applications**

- Multi-Function Peripherals

- Facsimile Equipment

- Flatbed or Handheld Color Scanners

- High-speed Document Scanner

- Independent Gain/Offset Correction for Each Channel

- Digital Black Level Correction Loop for Each Channel

- Programmable Input Clamp Voltage

- Flexible CCD/CIS Sensor Timing Generator

## **Key Specifications**

■ Maximum Input Level 1.2 or 2.4 Volt Modes

■ (both with + or - polarity option)

■ ADC Resolution 16-Bit

■ ADC Sampling Rate 45 MSPS

■ INL +/- 23 LSB (typ)

■ Channel Sampling Rate 15/22.5/30 MSPS

■ PGA Gain Steps 256 Steps

■ PGA Gain Range■ Analog DAC Resolution0.7 to 7.84x■ +/-9 Bits

■ Analog DAC Range +/-300mV or +/-600mV

■ Digital DAC Resolution +/-6 Bits

■ Digital DAC Range -1024 LSB to + 1008 LSB

■ SNR -74dB (@0dB PGA Gain)

■ Power Dissipation 505mW (LVDS) 610mW (CMOS)

■ Operating Temp 0 to 70°C

Supply Voltage

3.3V Nominal (3.0V to 3.6V range)

#### **Features**

- LVDS/CMOS Outputs

- LVDS/CMOS Pixel Rate Input Clock or ADC Input Clock

- CDS or S/H Processing for CCD or CIS sensors

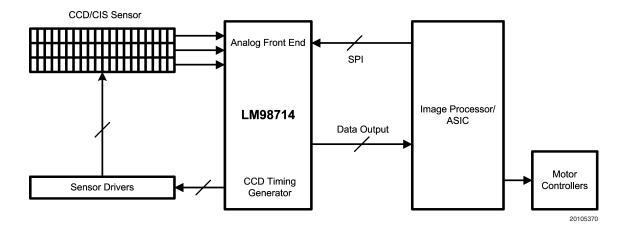

# System Block Diagram

FIGURE 1. Chip Block Diagram

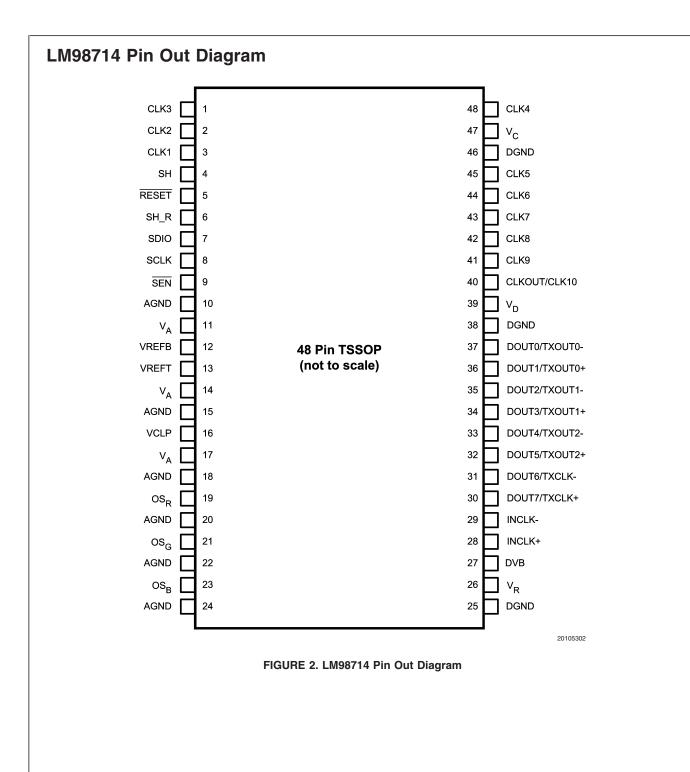

# **Pin Descriptions**

| Pin | Name            | I/O | Тур | Res | Description                                                                                                                                             |

|-----|-----------------|-----|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | CLK3            | 0   | D   | PU  | Configurable sensor control output.                                                                                                                     |

| 2   | CLK2            | 0   | D   | PD  | Configurable sensor control output.                                                                                                                     |

| 3   | CLK1            | 0   | D   | PU  | Configurable sensor control output.                                                                                                                     |

| 4   | SH              | 0   | D   | PD  | Sensor - Shift or transfer control signal for CCD and CIS sensors.                                                                                      |

| 5   | RESET           | ı   | D   | PU  | Active-low master reset. NC when function not being used.                                                                                               |

| 6   | SH_R            | ı   | D   | PD  | External request for an SH pulse.                                                                                                                       |

| 7   | SDIO            | I/O | D   |     | Serial Interface Data Input                                                                                                                             |

| 8   | SCLK            | I   | D   | PD  | Serial Interface shift register clock.                                                                                                                  |

| 9   | SEN             | I   | D   | PU  | Active-low chip enable for the Serial Interface.                                                                                                        |

| 10  | AGND            |     | Р   |     | Analog ground return.                                                                                                                                   |

| 11  | V <sub>A</sub>  |     | Р   |     | Analog power supply. Bypass voltage source with 4.7 $\mu$ F and pin with 0.1 $\mu$ F to AGND.                                                           |

| 12  | VREFB           | 0   | Α   |     | Bottom of ADC reference. Bypass with a 0.1µF capacitor to ground.                                                                                       |

| 13  | VREFT           | 0   | Α   |     | Top of ADC reference. Bypass with a 0.1µF capacitor to ground.                                                                                          |

| 14  | V <sub>A</sub>  |     | Р   |     | Analog power supply. Bypass voltage source with 4.7 $\mu$ F and pin with 0.1 $\mu$ F to AGND.                                                           |

| 15  | AGND            |     | Р   |     | Analog ground return.                                                                                                                                   |

| 16  | VCLP            | 10  | Α   |     | Input Clamp Voltage. Normally bypassed with a 0.1µF, and a 4.7µF capacitor to                                                                           |

|     |                 |     |     |     | AGND. An external reference voltage may be applied to this pin.                                                                                         |

| 17  | V <sub>A</sub>  |     | Р   |     | Analog power supply. Bypass voltage source with 4.7µF and pin with 0.1µF to AGND.                                                                       |

| 18  | AGND            |     | Р   |     | Analog ground return.                                                                                                                                   |

| 19  | OS <sub>R</sub> | I   | Α   |     | Analog input signal. Typically sensor Red output AC-coupled thru a capacitor.                                                                           |

| 20  | AGND            |     | Р   |     | Analog ground return.                                                                                                                                   |

| 21  | OS <sub>G</sub> | Ι   | Α   |     | Analog input signal. Typically sensor Green output AC-coupled thru a capacitor.                                                                         |

| 22  | AGND            |     | Р   |     | Analog ground return.                                                                                                                                   |

| 23  | OS <sub>B</sub> | I   | Α   |     | Analog input signal. Typically sensor Blue output AC-coupled thru a capacitor.                                                                          |

| 24  | AGND            |     | Р   |     | Analog ground return.                                                                                                                                   |

| 25  | DGND            |     | Р   |     | Digital ground return.                                                                                                                                  |

| 26  | V <sub>R</sub>  |     | Р   |     | Power supply input for internal voltage reference generator. Bypass this supply pin with a 0.1µF capacitor.                                             |

| 27  | DVB             | 0   | Р   |     | Digital Core Voltage bypass. Not an input. Bypass with 0.1µF capacitor to DGND.                                                                         |

| 28  | INCLK+          | ı   | D   |     | Clock Input. Non-Inverting input for LVDS clocks or CMOS clock input. CMOS clock is selected when pin 29 is held at DGND, otherwise clock is configured |

|     |                 |     |     |     | for LVDS operation.                                                                                                                                     |

| 29  | INCLK-          | h   | D   |     | Clock Input. Inverting input for LVDS clocks, connect to DGND for CMOS clock.                                                                           |

| 30  | DOUT7/          | 0   | D   |     | Bit 7 of the digital video output bus in CMOS Mode, LVDS Frame Clock+ in                                                                                |

|     | TXCLK+          |     |     |     | LVDS Mode.                                                                                                                                              |

| 31  | DOUT6/          | 0   | D   |     | Bit 6 of the digital video output bus in CMOS Mode, LVDS Frame Clock- in                                                                                |

|     | TXCLK-          |     |     |     | LVDS Mode.                                                                                                                                              |

| 32  | DOUT5/          | 0   | D   |     | Bit 5 of the digital video output bus in CMOS Mode, LVDS Data Out2+ in LVDS                                                                             |

|     | TXOUT2+         |     |     |     | Mode.                                                                                                                                                   |

| 33  | DOUT4/          | 0   | D   |     | Bit 4 of the digital video output bus in CMOS Mode, LVDS Data Out2- in LVDS                                                                             |

|     | TXOUT2-         |     |     |     | Mode.                                                                                                                                                   |

| 34  | DOUT3/          | 0   | D   |     | Bit 3 of the digital video output bus in CMOS Mode, LVDS Data Out1+ in LVDS                                                                             |

|     | TXOUT1+         |     |     |     | Mode.                                                                                                                                                   |

| 35  | DOUT2/          | 0   | D   |     | Bit 2 of the digital video output bus in CMOS Mode, LVDS Data Out1- in LVDS                                                                             |

|     | TXOUT1-         | 1   |     |     | Mode.                                                                                                                                                   |

# Pin Descriptions (Continued)

| Pin | Name           | I/O | Тур | Res | Description                                                                    |

|-----|----------------|-----|-----|-----|--------------------------------------------------------------------------------|

| 36  | DOUT1/         | 0   | D   |     | Bit 1 of the digital video output bus in CMOS Mode, LVDS Data Out0+ in LVDS    |

|     | TXOUT0+        |     |     |     | Mode.                                                                          |

| 37  | DOUT0/         | 0   | D   |     | Bit 0 of the digital video output bus in CMOS Mode, LVDS Data Out0- in LVDS    |

|     | TXOUT0-        |     |     |     | Mode.                                                                          |

| 38  | DGND           |     | Р   |     | Digital ground return.                                                         |

| 39  | V <sub>D</sub> |     | Р   |     | Power supply for the digital circuits. Bypass this supply pin with 0.1µF       |

|     |                |     |     |     | capacitor. A single 4.7µF capacitor should be used between the supply and the  |

|     |                |     |     |     | VD, VR and VC pins.                                                            |

| 40  | CLKOUT/        | 0   | D   | PD  | Output clock for registering output data when using CMOS outputs, or           |

|     | CLK10          |     |     |     | configurable sensor control output.                                            |

| 41  | CLK9           | 0   | D   | PD  | Configurable sensor control output.                                            |

| 42  | CLK8           | 0   | D   | PD  | Configurable sensor control output.                                            |

| 43  | CLK7           | 0   | D   | PD  | Configurable sensor control output.                                            |

| 44  | CLK6           | 0   | D   | PU  | Configurable sensor control output.                                            |

| 45  | CLK5           | 0   | D   | PD  | Configurable sensor control output.                                            |

| 46  | DGND           |     | Р   |     | Digital ground return.                                                         |

| 47  | V <sub>C</sub> |     | Р   |     | Power supply for the sensor control outputs. Bypass this supply pin with 0.1µF |

|     |                |     |     |     | capacitor.                                                                     |

| 48  | CLK4           | 0   | D   | PD  | Configurable sensor control output.                                            |

(I=Input), (O=Output), (IO=Bi-directional), (P=Power), (D=Digital), (A=Analog), (PU=Pull Up with an internal resistor), (PD=Pull Down with an internal resistor.).

# **Absolute Maximum Ratings** (Notes 2,

1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (VA,VR,VD,VC)        | 4.2V        |

|-------------------------------------|-------------|

| Voltage on Any Input Pin            | -0.3V to    |

| (Not to exceed 4.2V)                | (VA + 0.3V) |

| Voltage on Any Output Pin           | -0.3V to    |

| (execpt DVB and not to exceed       | (VA + 0.3V) |

| 4.2V)                               |             |

| DVB Output Pin Voltage              | 2.0V        |

| Input Current at any pin other than | ±25 mA      |

Supply Pins (Note 3)

Package Input Current (except

Supply Pins) (Note 3)

Maximum Junction Temperature (TA)

| Thermal Resistance $(\theta_{JA})$           | 66°C/W |

|----------------------------------------------|--------|

| Package Dissipation at T <sub>A</sub> = 25°C | 1.89W  |

ESD Rating (Note 5)

Human Body Model 2500V

Machine Model 250V

Storage Temperature -65°C to +150°C

Soldering process must comply with National

Semiconductor's Reflow Temperature Profile

specifications. Refer to www.national.com/packaging.

(Note 6)

(Note 4)

# Operating Ratings (Notes 1, 2)

Operating Temperature Range  $0^{\circ}\text{C} \le \text{T}_{\text{A}} \le +70^{\circ}\text{C}$ All Supply Voltage +3.0V to +3.6V

#### **Electrical Characteristics**

The following specifications apply for VA = VD = VR = VC = 3.3V,  $C_L$  = 10pF, and  $f_{INCLK}$  = 15MHz unless otherwise specified. Boldface limits apply for  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A$  = 25°C.

±50 mA

150°C

|                  |                                    |                                    |          | Тур      |      |       |

|------------------|------------------------------------|------------------------------------|----------|----------|------|-------|

| Symbol           | Parameter                          | Conditions                         | Min      | (Note 8) | Max  | Units |

| CMOS Digi        | tal Input DC Specifications (RESE  | Tb, SH_R, SCLK, SENb)              |          |          |      |       |

| $V_{IH}$         | Logical "1" Input Voltage          |                                    | 2.0      |          |      | V     |

| V <sub>IL</sub>  | Logical "0" Input Voltage          |                                    |          |          | 0.8  | V     |

| I <sub>IH</sub>  | Logical "1" Input Current          | V <sub>IH</sub> = VD               |          |          |      |       |

|                  |                                    | RESET                              |          | 235      |      | nA    |

|                  |                                    | SH_R, SCLK                         |          | 70       |      | μA    |

|                  |                                    | SEN                                |          | 130      |      | nA    |

| I <sub>IL</sub>  | Logical "0" Input Current          | VIL = DGND                         |          |          |      |       |

|                  |                                    | RESET                              |          | 70       |      | μA    |

|                  |                                    | SH_R, SCLK                         |          | 235      |      | nA    |

|                  |                                    | SEN                                |          | 70       |      | μA    |

| CMOS Digi        | tal Output DC Specifications (SH,  | CLK1 to CLK10, CMOS Data C         | outputs) |          |      | 1     |

| V <sub>OH</sub>  | Logical "1" Output Voltage         | I <sub>OUT</sub> = -0.5mA          | 2.95     |          |      | V     |

| V <sub>OL</sub>  | Logical "0" Output Voltage         | I <sub>OUT</sub> = 1.6mA           |          |          | 0.25 | V     |

| I <sub>os</sub>  | Output Short Circuit Current       | V <sub>OUT</sub> = DGND            |          | 16       |      | mA    |

|                  |                                    | V <sub>OUT</sub> = VD              |          | -20      |      |       |

| l <sub>oz</sub>  | CMOS Output TRI-STATE              | V <sub>OUT</sub> = DGND            |          | 20       |      | nA    |

|                  | Current                            | $V_{OUT} = VD$                     |          | -25      |      |       |

| CMOS Digi        | tal Input/Output DC Specifications | s (SDIO)                           | •        |          |      | 1     |

| I <sub>IH</sub>  | Logical "1" Input Current          | V <sub>IH</sub> = VD               |          | 90       |      | nA    |

| I <sub>IL</sub>  | Logical "0" Input Current          | V <sub>IL</sub> = DGND             |          | 90       |      | nA    |

| LVDS/CMO         | S Clock Receiver DC Specification  | ns (INCLK+ and INCLK- Pins)        | •        |          |      | •     |

| V <sub>IHL</sub> | Differential LVDS Clock            | R <sub>L</sub> = 100W              |          |          | 100  | mV    |

|                  | High Threshold Voltage             | V <sub>CM</sub> (LVDS Input Common |          |          |      |       |

|                  |                                    | Mode Voltage)= 1.25V               |          | <u> </u> |      |       |

| V <sub>ILL</sub> | Differential LVDS Clock            |                                    | -100     |          |      | mV    |

|                  | Low Threshold Voltage              |                                    |          |          |      |       |

**Electrical Characteristics** (Continued)

The following specifications apply for VA = VD = VR = VC = 3.3V,  $C_L = 10pF$ , and  $f_{INCLK} = 15MHz$  unless otherwise specified. **Boldface limits apply for T\_A = T\_{MIN} to T\_{MAX};** all other limits  $T_A = 25^{\circ}C$ .

| 0                | Daywooday                            | O a sa distinue                 | NA:  | Тур      |      | 11-4- |

|------------------|--------------------------------------|---------------------------------|------|----------|------|-------|

| Symbol           | Parameter                            | Conditions                      | Min  | (Note 8) | Max  | Units |

| $V_{IHC}$        | CMOS Clock<br>High Threshold Voltage | INCLK- = DGND                   | 2.0  |          |      | V     |

| V <sub>ILC</sub> | CMOS Clock                           |                                 |      |          | 0.8  | V     |

| iLO              | Low Threshold Voltage                |                                 |      |          |      |       |

| I <sub>IHL</sub> | CMOS Clock                           |                                 |      |          | 280  | μΑ    |

|                  | Input High Current                   |                                 |      |          |      |       |

| I <sub>ILC</sub> | CMOS Clock                           |                                 |      |          | -150 | μA    |

|                  | Input Low Current                    |                                 |      |          |      |       |

| LVDS Outp        | out DC Specifications                |                                 |      |          |      | 1     |

| V <sub>OD</sub>  | Differential Output Voltage          | $R_L = 100\Omega$               | 180  | 328      | 450  | mV    |

| V <sub>os</sub>  | LVDS Output Offset Voltage           | _                               | 1.17 | 1.23     | 1.3  | V     |

| I <sub>os</sub>  | Output Short Circuit Current         | $V_{OUT} = 0V, R_L = 100\Omega$ |      | 7.9      |      | mA    |

|                  | ply Specifications                   |                                 |      |          |      | 1     |

| IA               | VA Analog Supply Current             | VA Normal State                 | 60   | 97       | 125  | mA    |

|                  | - ''                                 | VA Low Power State              | 12   | 23       | 32   | mA    |

|                  |                                      | (Powerdown)                     |      |          |      |       |

| IR               | VR Digital Supply Current            | VR Normal State                 | 30   | 64       | 75   | mA    |

|                  |                                      | (LVDS Outputs)                  |      |          |      |       |

|                  |                                      | CMOS Output Data Format         | 15   | 47       | 55   | mA    |

|                  |                                      | LVDS Output Data Format         |      | 47       |      | mA    |

|                  |                                      | with Data Outputs Disabled      |      |          |      |       |

| ID               | VD Digital Output Driver Supply      | LVDS Output Data Format         |      | 0.05     |      | mA    |

|                  | Current                              | CMOS Output Data Format         | 12   |          | 40   | mA    |

|                  |                                      | (ATE Loading of CMOS            |      |          |      |       |

|                  |                                      | Outputs > 50pF)                 |      |          |      |       |

| IC               | VC CCD Timing Generator              | Typical sensor outputs:         | 0.5  |          | 12   | mA    |

|                  | Output Driver Supply Current         | SH, CLK1=Φ1A, CLK2=Φ2A,         |      |          |      |       |

|                  |                                      | CLK3=ФВ, CLK4=ФС,               |      |          |      |       |

|                  |                                      | CLK5=RS, CLK6=CP                |      |          |      |       |

|                  |                                      | (ATE Loading of CMOS            |      |          |      |       |

|                  |                                      | Outputs > 50pF)                 |      |          |      |       |

| PWR              | Average Power Dissipation            | LVDS Output Data Format         | 350  | 505      | 650  | mW    |

|                  |                                      | CMOS Output Data Format         | 380  | 610      | 700  | mW    |

|                  |                                      | (ATE Loading of CMOS            |      |          |      |       |

|                  |                                      | Outputs > 50pF)                 |      |          |      |       |

| Input Samp       | oling Circuit Specifications         |                                 |      |          |      |       |

| V <sub>IN</sub>  | Input Voltage Level                  | CDS Gain=1x, PGA Gain=1x        |      | 2.3      |      | Vp-p  |

|                  |                                      | CDS Gain=2x, PGA Gain=          |      | 1.22     |      |       |

|                  |                                      | 1x                              |      |          |      |       |

Electrical Characteristics (Continued)

The following specifications apply for VA = VD = VR = VC = 3.3V, C<sub>L</sub> = 10pF, and f<sub>INCLK</sub> = 15MHz unless otherwise specified.

Boldface limits apply for T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>; all other limits T<sub>A</sub> = 25°C.

|                     |                                                   |                                                                                                                                                      |                 | Тур                |                 |           |

|---------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------|-----------------|-----------|

| Symbol              | Parameter                                         | Conditions                                                                                                                                           | Min             | (Note 8)           | Max             | Units     |

| I <sub>IN_SH</sub>  | Sample and Hold Mode                              | Source Followers Off                                                                                                                                 | 50              |                    | 70              | μΑ        |

|                     | Input Leakage Current                             | CDS Gain = 1x                                                                                                                                        | (-70)           |                    | (-40)           |           |

|                     |                                                   | $OS_X = VA (OS_X = AGND)$                                                                                                                            |                 |                    |                 |           |

|                     |                                                   | Source Followers Off                                                                                                                                 | 75              |                    | 105             | μA        |

|                     |                                                   | CDS Gain = 2x                                                                                                                                        | (-105)          |                    | (-75)           |           |

|                     |                                                   | $OS_X = VA (OS_X = AGND)$                                                                                                                            | , ,             |                    | , ,             |           |

|                     |                                                   | Source Followers On                                                                                                                                  | -200            | -10                | 200             | nA        |

|                     |                                                   | CDS Gain = 2x                                                                                                                                        |                 | -16                |                 |           |

|                     |                                                   | $OS_X = VA (OS_X = AGND)$                                                                                                                            |                 |                    |                 |           |

| C <sub>SH</sub>     | Sample/Hold Mode                                  | CDS Gain = 1x                                                                                                                                        |                 | 2.5                |                 | pF        |

| OSH                 | Equivalent Input Capacitance                      | ODS Gain = 1x                                                                                                                                        |                 | 2.5                |                 | ρı        |

|                     |                                                   | CDS Coin Ov                                                                                                                                          |                 | 4                  |                 | nF        |

| 1                   | (see Figure 11)                                   | CDS Gain = 2x                                                                                                                                        | 000             | 4                  | 000             | pF        |

| I <sub>IN_CDS</sub> | CDS Mode                                          | Source Followers Off                                                                                                                                 | -300            | 7                  | 300             | nA        |

|                     | Input Leakage Current                             | $OS_X = VA (OS_X = AGND)$                                                                                                                            |                 | (-25)              |                 | _         |

| $R_{CLPIN}$         | CLPIN Switch Resistance                           |                                                                                                                                                      |                 | 16                 | 50              | Ω         |

|                     | (OS <sub>X</sub> to VCLP Node in Figure 8)        |                                                                                                                                                      |                 |                    |                 |           |

| CLP Refe            | erence Circuit Specifications                     |                                                                                                                                                      |                 |                    |                 |           |

|                     | VCLP DAC Resolution                               |                                                                                                                                                      |                 | 4                  |                 | Bits      |

|                     | VCLP DAC Step Size                                |                                                                                                                                                      |                 | 0.16               |                 | V         |

| V <sub>VCLP</sub>   | VCLP DAC Voltage Min Output                       | VCLP Config. Register =                                                                                                                              | 0.14            | 0.26               | 0.43            | V         |

|                     |                                                   | 0001 0000b                                                                                                                                           |                 |                    |                 |           |

|                     | VCLP DAC Voltage Max Output                       | VCLP Config. Register =                                                                                                                              | 2.38            | 2.68               | 2.93            | V         |

|                     |                                                   | 0001 1111b                                                                                                                                           |                 |                    |                 |           |

|                     | Resistor Ladder Enabled                           | VCLP Config. Register =                                                                                                                              | 1.54            | V <sub>A</sub> / 2 | 1.73            | V         |

|                     |                                                   | 0010 xxxxb                                                                                                                                           |                 |                    |                 |           |

| I <sub>SC</sub>     | VCLP DAC Short Circuit Output                     | VCLP Config. Register =                                                                                                                              |                 | 30                 |                 | mA        |

| isc                 | Current                                           | 0001 xxxxb                                                                                                                                           |                 |                    |                 | ША        |

| Black I ove         | el Offset DAC Specifications                      | 0001 XXXXD                                                                                                                                           |                 |                    |                 |           |

| DIACK LEVE          | Resolution                                        |                                                                                                                                                      |                 | 10                 |                 | Dito      |

|                     |                                                   |                                                                                                                                                      |                 |                    |                 | Bits      |

|                     | Monotonicity                                      | 00000                                                                                                                                                | G               | uaranteed by       | cnaracterizat   | ion       |

|                     | Offset Adjustment Range                           | CDS Gain = 1x                                                                                                                                        |                 |                    |                 |           |

|                     | Referred to AFE Input                             | Minimum DAC Code =                                                                                                                                   |                 | -614               |                 |           |

|                     |                                                   |                                                                                                                                                      |                 |                    |                 | mV        |

|                     |                                                   | 0x000                                                                                                                                                |                 |                    |                 |           |

|                     |                                                   | Maximum DAC Code =                                                                                                                                   |                 | 614                |                 |           |

|                     |                                                   | Maximum DAC Code = 0x3FF                                                                                                                             |                 | 614                |                 |           |

|                     |                                                   | Maximum DAC Code =                                                                                                                                   |                 | 614                |                 |           |

|                     |                                                   | Maximum DAC Code =  0x3FF  CDS Gain = 2x  Minimum DAC Code =                                                                                         |                 | -307               |                 |           |

|                     |                                                   | Maximum DAC Code = 0x3FF  CDS Gain = 2x                                                                                                              |                 | -                  |                 | mV        |

|                     |                                                   | Maximum DAC Code =  0x3FF  CDS Gain = 2x  Minimum DAC Code =                                                                                         |                 | -                  |                 |           |

|                     |                                                   | Maximum DAC Code =  0x3FF  CDS Gain = 2x  Minimum DAC Code =  0x000                                                                                  |                 | -307               |                 |           |

|                     | Offset Adjustment Range                           | Maximum DAC Code =  0x3FF  CDS Gain = 2x  Minimum DAC Code =  0x000  Maximum DAC Code =  0x3FF  Minimum DAC Code =                                   | -16000          | -307               | -18200          |           |

|                     | Offset Adjustment Range                           | Maximum DAC Code =  0x3FF  CDS Gain = 2x  Minimum DAC Code =  0x000  Maximum DAC Code =  0x3FF                                                       | -16000          | -307               | -18200          | mV        |

|                     | Offset Adjustment Range<br>Referred to AFE Output | Maximum DAC Code =  0x3FF  CDS Gain = 2x  Minimum DAC Code =  0x000  Maximum DAC Code =  0x3FF  Minimum DAC Code =                                   | -16000<br>16000 | -307               | -18200<br>18200 |           |

|                     |                                                   | Maximum DAC Code =  0x3FF  CDS Gain = 2x  Minimum DAC Code =  0x000  Maximum DAC Code =  0x3FF  Minimum DAC Code =  0x000                            |                 | -307               |                 | mV        |

|                     |                                                   | Maximum DAC Code =  0x3FF  CDS Gain = 2x  Minimum DAC Code =  0x000  Maximum DAC Code =  0x3FF  Minimum DAC Code =  0x000  Maximum DAC Code =        |                 | -307               |                 | mV        |

|                     | Referred to AFE Output                            | Maximum DAC Code =  0x3FF  CDS Gain = 2x  Minimum DAC Code =  0x000  Maximum DAC Code =  0x3FF  Minimum DAC Code =  0x000  Maximum DAC Code =  0x3FF |                 | -307<br>307        |                 | mV<br>LSB |

## **Electrical Characteristics** (Continued)

The following specifications apply for VA = VD = VR = VC = 3.3V,  $C_L = 10 pF$ , and  $f_{INCLK} = 15 MHz$  unless otherwise specified. Boldface limits apply for  $T_A = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = 25 \,^{\circ}C$ .

|                     |                                  |                         |              | Тур          |              |       |

|---------------------|----------------------------------|-------------------------|--------------|--------------|--------------|-------|

| Symbol              | Parameter                        | Conditions              | Min          | (Note 8)     | Max          | Units |

| INL                 | Integral Non-Linearity           |                         | -3.1         |              | 2.65         | LSB   |

| PGA Spec            | ifications                       |                         |              |              |              |       |

|                     | Gain Resolution                  |                         |              | 8            |              | Bits  |

|                     | Monotonicity                     |                         | G            | uaranteed by | characteriza | tion  |

|                     | Maximum Gain                     | CDS Gain = 1x           | 7.18         | 7.9          | 8.77         | V/V   |

|                     |                                  | CDS Gain = 1x           | 17.1         | 17.9         | 18.9         | dB    |

|                     | Minimum Gain                     | CDS Gain = 1x           | 0.56         | 0.7          | 0.82         | V/V   |

|                     |                                  | CDS Gain = 1x           | -5           | -3           | -1.72        | dB    |

|                     | PGA Function                     | Gain (V/\               | /) = (196/(2 | 280-PGA Code | e))          |       |

|                     |                                  | Gain (dB) = 2           | 0LOG10(1     | 96/(280-PGA  | Code))       |       |

|                     | Channel Matching                 | Minimum PGA Gain        |              | 3            |              | %     |

|                     |                                  | Maximum PGA Gain        |              | 12.7         |              |       |

| ADC Spec            | ifications                       |                         |              |              |              |       |

| V <sub>REFT</sub>   | Top of Reference                 |                         |              | 2.07         |              | V     |

| $V_{REFB}$          | Bottom of Reference              |                         |              | 0.89         |              | V     |

| V <sub>REFT</sub> - | Differential Reference Voltage   |                         | 1.07         | 1.18         | 1.29         | V     |

|                     | Overrange Output Code            |                         |              | 65535        |              |       |

|                     | Underrange Output Code           |                         |              | 0            |              |       |

| Digital Off         | set "DAC" Specifications         |                         |              |              |              | 1     |

|                     | Resolution                       |                         |              | 7            |              | Bits  |

|                     | Digital Offset DAC LSB Step Size | Referred to AFE Output  |              | 16           |              | LSB   |

|                     | Offset Adjustment Range          | Min DAC Code =7b0000000 |              | -1024        |              |       |

|                     | Referred to AFE Output           | Mid DAC Code =7b1000000 |              | 0            |              | 1.00  |

|                     |                                  | Max DAC Code =          |              | 1008         |              | LSE   |

|                     |                                  | 7b1111111               |              |              |              |       |

| Full Chani          | nel Performance Specifications   |                         |              |              |              |       |

| DNL                 | Differential Non-Linearity       |                         | -0.99        | 0.8/-0.6     | 2.55         | LSB   |

| INL                 | Integral Non-Linearity           |                         | -73          | +/-23        | 78           | LSB   |

| SNR                 | Total Output Noise               | Minimum PGA Gain        |              | -79          |              | dB    |

|                     |                                  |                         |              | 7.2          |              | LSE   |

|                     |                                  |                         |              |              |              | RMS   |

|                     |                                  | PGA Gain = 1x           |              | -74          |              | dB    |

|                     |                                  |                         |              | 13           | 30           | LSE   |

|                     |                                  |                         |              |              |              | RMS   |

|                     |                                  | Maximum PGA Gain        |              | -56          |              | dB    |

|                     |                                  |                         |              | 104          | <u> </u>     | LSE   |

|                     |                                  |                         |              |              |              | RMS   |

|                     | Channel to Channel Crosstalk     | Mode 3                  |              | 47           |              | LSB   |

|                     |                                  | Mode 2                  |              | 16           |              |       |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the Operating Ratings is not recommended.

Note 2: All voltages are measured with respect to AGND = DGND = 0V, unless otherwise specified.

Note 3: When the input voltage  $(V_{IN})$  at any pin exceeds the power supplies  $(V_{IN} < GND \text{ or } V_{IN} > V_A \text{ or } V_D)$ , the current at that pin should be limited to 25 mA. The 50 mA maximum package input current rating limits the number of pins that can simultaneously safely exceed the power supplies with an input current of 25 mA to two.

Note 4: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$  and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any temperature is  $P_D = (T_{JMAX} - T_A)/\theta_{JA}$ . The values for maximum power dissipation listed above will be reached only when the device is operated in a severe fault condition (e.g. when input or output pins are driven beyond the power supply voltages, or the power supply polarity is reversed). Such conditions should always be avoided.

Note 5: Human body model is 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor. Machine model is 220 pF discharged through  $0\Omega$ .

Note 6: Reflow temperature profiles are different for lead-free and non-lead-free packages.

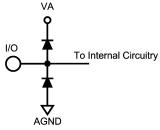

Note 7: The analog inputs are protected as shown below. Input voltage magnitudes beyond the supply rails will not damage the device, provided the current is limited per note 3. However, input errors will be generated If the input goes above VA and below AGND.

20105371

Note 8: Typical figures are at  $T_A = 25^{\circ}C$ , and represent most likely parametric norms at the time of product characterization. The typical specifications are not guaranteed.

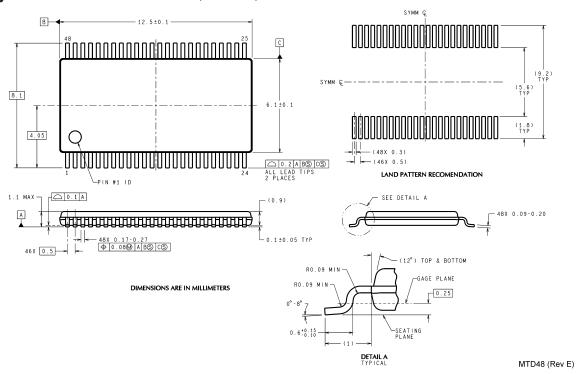

### Physical Dimensions inches (millimeters) unless otherwise noted

48-Lead TSSOP NS Package Number MTD48

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor follows the provisions of the Product Stewardship Guide for Customers (CSP-9-111C2) and Banned Substances and Materials of Interest Specification (CSP-9-111S2) for regulatory environmental compliance. Details may be found at: www.national.com/quality/green.

Lead free products are RoHS compliant.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560